這篇全名為Analysis-by-Synthesis/Overlap-Add Sinusoidal Modeling Applied to the Analysis and Synthesis of Musical Tones,是1992年AES的Journal,主要精神在於Analysis-by-Synthesis,概念其實跟 codec 的 encoder 內部包 decoder 很像,它每一圈都會找一個新的 Sinusoid並加入,以致於原訊號扣掉這些Sinusoids後會最小,最後再依照這些Sinusoids來分析下次要找的參數。

本週我報告了ABS流程及公式推導,老師提出了一個問題。

在計算 least square error 時,ω 如果照 paper 上說的只是將每個frequency bin代進去看誰最小,這個動作不就跟做DFT一樣?如果該訊號的頻率介於兩個bin之間又該如何?

論文 p501 第(25)式說明他是用每個bin代進去算的,後面我還沒報告的部份裡有另一個主要觀念 Quasi-Harmonic Modeling 則只有調整 partials 的位置,但前題是 f0 要找得準,其他部份要全部看懂後才能確定它是否沒做特殊處理。

而老師提出一個解決此問題的方向…

既然公式中原本只對 a 跟 b 做微分取極值,我們可以對 cos(ωn) 與 sin(ωn) 先做 Taylor expansion 後對ω做微分取極值,極值不只一個解,先前我們可以知道ω落在哪些bin之間,以此做判斷選出正確的極值即可。

Dec. 9th. 2008 update

上次提到「ω 如果照 paper 上說的只是將每個frequency bin代進去看誰最小,這個動作不就跟做DFT一樣?」的問題,其實在論文上有說明 M 值可自訂,M 值 & Na(Analysis frame size) 與 SNR 的關係可在投影片上看到。之前之所以誤會成是 frame size 是因為 M 同時也是 DFT 的慣用標號,論文第三章的實作說明中只有一小句話有提到原始訊號轉 DFT 前需先 zero padding 到 M 的大小。

Download: slide

Jan. 6th. 2009 update

今天回報已解決bugs及目前遇到的問題。投影片中有列出 4 個case,接下來打算先針對第二個case去找問題所在,這是沒有套用windows function,但FFT size有加長的結果,很明顯phase跑掉了。

Download: slide

Jan. 13th. 2009 update

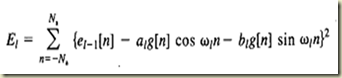

由於 revise 原本論文的算式已找不出錯誤,某天我翻出同作者在五年後發的另一篇論文:Speech Analysis/Synthesis and Modification Using an Analysis-by-Synthesis/Overlap-Add Sinusoidal Model,雖然這兩篇論文內容極為相似,不過我發現有部份算式不一樣,舊論文在推導MSE時使用

新論文則是用

換了新論文的算式,套上pure sine後結果很正確 (case 4-4),很開心的套用到 violin 第一個frame也正確,但跑到第四個frame時便找錯頻率了 (case 4-5)。也因為如此,找出了另一個主要問題。

論文在反推phase時是用 -arctan(bi/ai),這是因為公式的推導中會出現 sinφ/cosφ,但是,原本φ的範圍是介於 0~2π,arctan的結果卻只會落在 +-0.5π,導致當我們用 cos 去製造 sinusoids 時,phase的平移範圍太小,當這個frame起始的幾個samples值是呈現遞減趨勢時,phase的誤差會剛好差π。解決的辦法就是改用 Matlab 的 angle function。(case 4-6)

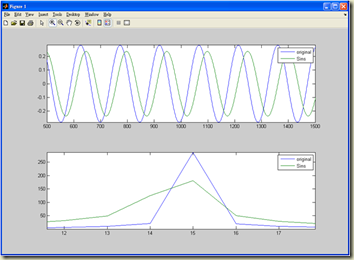

最後,實驗結果還是有phase的偏移,所以開始針對phase再開新的case來討論。目前的問題出在:在找第一個 sin 時是正確的,找第二個時 phase 便會出錯,可參考 case 5-2,第一個 sin 的frequency index落在 14, 15, 16,第二個在 17, 18, 19。中間的圖說明能量上跟原訊號是很完美的貼近,但下圖的 phase 卻跑掉,導致上圖的波形有所差異。

Download: slide

2008年, 我教的這屆學生要畢業, 其實我自這屆以後, 大學部我開的都是選修課, 所以跟學生的關係不再似以前一樣密切, 不過我在每屆學生畢業照之時, 一定會抽空參加.

這系的老師不知怎地, 不太參加學生的活動, 甚至連畢業照show up的老師也不多. 師生的關係疏離嚴重. 我想跟老師的研究升等壓力超大有關吧! 也怪不得老師們, 我見到系上的新老師通常來不到一年, 其氣色與健康就走下坡的很多, 這也令人憂心. 教育事業走到這一步, 不知道該怪誰, 不知道該怎麼說與怎麼辦?

話說2008畢業照, 一班在星期五 , 另一班竟然定在星期六, 星期五參加的人都少了, 星期六一定更慘. 我是周末一定要陪家人的, 何況內人星期六到北部開會, 留我一個人要搞定兩個孩子, 出門對我來說簡直是恐怖與不可能的任務. 所以我只答應星期五出現, 星期六的就抱歉了.

沒想到我星期五的時間記錯了, 一點記成兩點, 等跑到圖書館錢已經曲終人散, 沒辦法, 我又不想缺席任一屆的畢業照, 星期六上午硬著頭皮出門.

出門前先幫Diane與Joanne洗一下屁屁, 10點開始餵午餐, 10點45分出門. 10點55分到學校. 11點多一點與學生會合.

大家可以想像到學生驚訝驚喜的樣子, 因為我事前沒說, 而當天也確實沒其他老師出席, 學生失望之極可想而知, 但是突然有一個老師出現, 心情可想而知, 何況還多了兩個如花似玉的小女生.

所以大家爭相跟我們三人拍照, 可惜我家Diane靦腆到家了, 所以一直沒太多笑容, 但是學生的滿足我可以感受到. 我想這會是我以及這一屆學生永生難忘的畢業照.

真的, 其實做老師的多用一點心, 事情總是會不一樣, 就像這2008的搞笑畢業照一樣.

其實我的心裡面也多少帶著一點心酸.

這是我跟我的專題生的合照. Diane跟Joanne在拍照後, 我待開他們後就開始恢復頑皮了, 玩得起勁得很, 挖勒! 一直玩到下午三點半才回家. 除了他們高興之外, 我也真的佩服自己.

一個字, 猛啦! ㄟ! 我是說Diane跟Joanne很猛, 不是我啦.

那天 !我累癱了.

一共有5個core

一共有5個core