--- [09.09.16] ------------------------------------------------

目前完成的部份是可以將一個簡單的加減法電路掛到CDK板子的FPGA上,並且可透過ICE Server讓Host (PC)存取這個加減法電路,也可讓CDK上的Linux透過Driver使一隻User Space的程式可以存取這個電路。

CDK上的FPGA是透過AHB或APB與其他的硬體作溝通,因此要在FPGA上實作電路必須要實做與AHB或APB溝通的interface,這個interface我是直接使用CDK所給的範例裡的,我只修改最底層的電路。

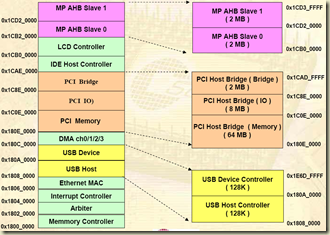

另外,照CDK的規格書所述,基本上我們可以在fpga上實作兩個Slave掛在AHB下,而Bus上的Memory Map是已經給定好的:

- Slave1是Map在0x1CB20000,大小為2MB

- Slave2是Map在0x1CD20000,大小為2MB

因此我透過範例的interface將電路實作在Slave1裡,讓其他硬體可透過0x1CB20000這個位址與其作溝通。

上面是利用ICE Server讓Host在CDK上跑一隻簡單的程式,其中紅框中的slavebase即是儲存0x1CB20000,然後就透過存取slavebase直接與FPGA的電路溝通。藍框中是執行的結果。

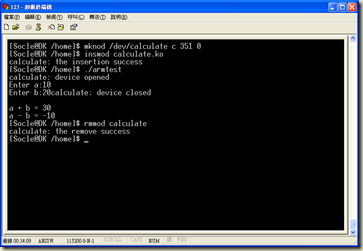

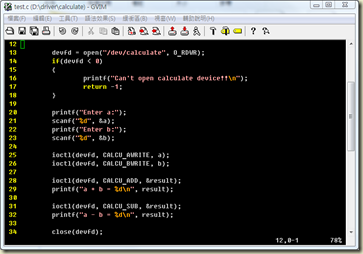

而上圖則是先在CDK上boot Linux後,利用我寫的簡單driver (calculate.ko)來讓armtest這隻程式可以輸入2個數值給電路來做相加和相減。基本上armteset是透過ioctl這個function來與硬體做溝通,程式碼如下,將Device打開就利用driver事先定義好的command發命令至driver,driver再根據command控制加減法電路。

再來應該是要做關於driver codegen的部份,但要寫codegen的話勢必要有一定程度至瞭解Linux driver,所以我想我應該要找個driver trace。

9 則留言:

範例中的Slave 完整度如何?

你所謂的完整度的意思是?

這是Gary做的東西的第一步, 都是Physical的. 還沒進到Cyber呢?

聽過人家講CPS嗎? Cyber Physical System (CPS), 你看人家多會取名字!!

其實我們也在做這件事, 不過最終是Physical system. 中間一堆tools要做. 有paper價值嗎? 大概不多, 寫兩篇conferences吧! 不過有用就是了.

文中提到 FPGA內AHB slave 的interface是套用範例電路的,我想瞭解的是這範例的完整度

Thx :)

我也想知道. Gary! 可以回一下嗎?

另外我們可以開始QEMU的東西了嗎?

抱歉,我不太懂怎樣才叫完整

範例中的slave是將rgb轉成yuv然後輸出,基本上是將資料寫到特定位址,接著電路會將之轉成yuv分別寫到3塊電路中的記憶體。

完整是指有做到哪些部份?

Gary,

我們想知道的是"AHB Slave Interface"是不是implement了AHB Protocol,又支援到什麼程度... ex. burst mode...etc...

不是範例電路的功能....

Gary, 可以回一下嗎? 我也想知道.

Android 的 HAL 技術

http://www.jollen.org/blog/2009/10/android-hal-status-report.html

gary...你上次報的好像有點out-of-date

再補充一下這個吧..

Gary, Update一下你的論文內容與進度吧!

張貼留言